# ECE 271, Design Project

# Nicholas Broce, Caden Friesen, Trevor Horine ${\it March~4,~2021}$

# Contents

|    | roject Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | IES Controller Input - Motor and Addressable LED Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | 2.2.1 NES Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | 2.2.2 Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    | 2.2.3 Synchronizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|    | 2.2.4 Countreset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    | 2.2.5 Neslatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | 2.2.6 Nesclk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 2.2.7 Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | 2.3.1 Colorcounter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2. | 4 Led                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    | 2.4.1 Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | 2.4.2 comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    | 2.4.3 syncronizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | 2.4.4 countreset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    | 2.4.5 Twenty Four Bit to Ninety Six Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    | 2.4.6 waveout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

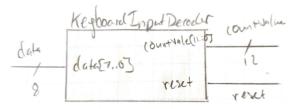

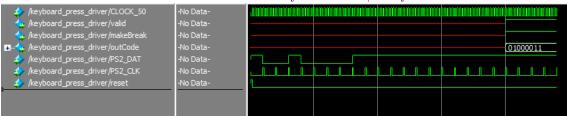

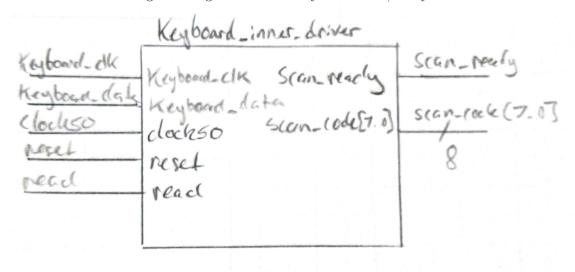

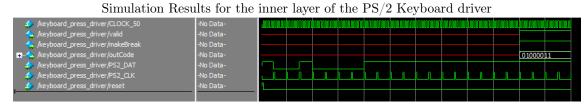

| 3  | 3.2.1 Individual Block 9 - keyboard_inner_driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

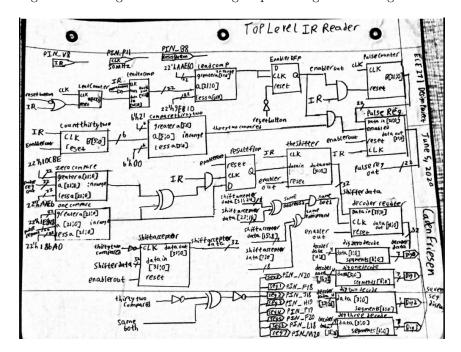

|    | nfrared Receiver Input - Seven Segment Display Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4. | r and the second |

| 4. | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4. | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4. | ı v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

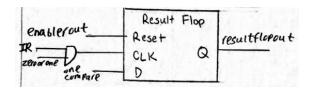

| 4. | 10 Individual Block 10 - Result Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

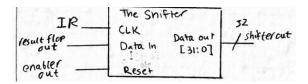

|   | 4.11 Individual Block 11 - The Shifter                               | 36 |

|---|----------------------------------------------------------------------|----|

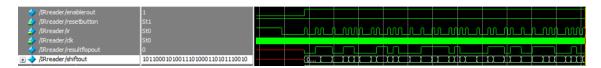

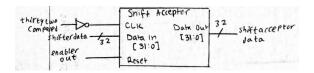

|   | 4.12 Individual Block 12 - Shift Acceptor                            | 36 |

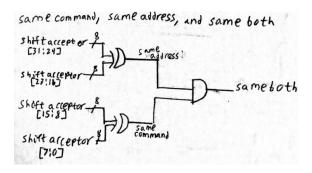

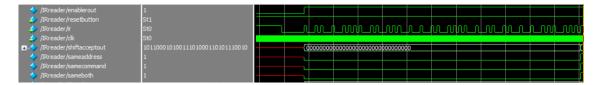

|   | 4.13 Individual Block 13 - Same command, Same Address, and Same Both | 37 |

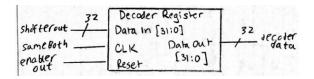

|   | 4.14 Individual Block 14 - Decoder Register                          | 38 |

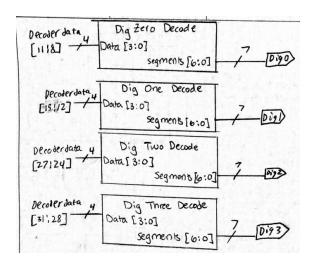

|   | 4.15 Individual Block 15 - Digzero decode through Digthree encode    | 38 |

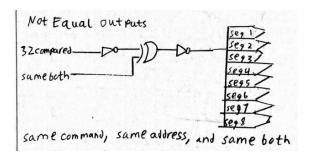

|   | 4.16 Individual Block 16 - Not Equal Outputs                         | 39 |

| A | SystemVerilog Files                                                  | 40 |

|   | A.1 NES Controller Input - Motor and Addressable LED Output          | 41 |

|   | A.2 PS/2 Keyboard Input - Square Wave Audio Output                   | 48 |

|   | A.3 Infrared Receiver Input - Seven Segment Display Output           | 53 |

| В | Simulation Files (Do scripts)                                        | 56 |

|   | B.1 NES Controller Input - Motor and Addressable LED Output          | 56 |

|   | B.2 PS/2 Keyboard Input - Square Wave Audio Output                   | 59 |

|   | B.3 Infrared Receiver Input - Seven Segment Display Output           | 60 |

# 1 Project Description

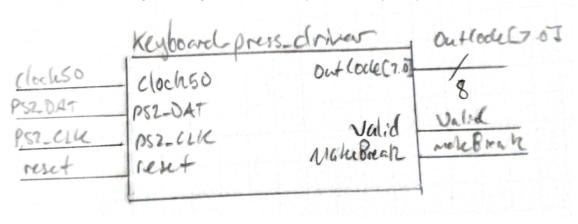

Inputs: The inputs for the entire project are clk50mhz, reset, nesdata, keyboarddata, clockkeyboard, resetkeyboard, and irdata. This project is split into three parts with three total input systems, those being the NES Controller, the PS/2 keyboard, and the IR remote signal, and each of those systems use the same 50MHz clock signal as a base input. This clock signal is either used as is or is altered with clock dividers in each of the sub-projects own files. Each of the three systems also share a common reset signal called reset. Nesdata and keyboard data operate very similarly to each other. Both are binary signals that are really a long signal of binary digits that denote a specific button or key depending on the controller inputted. The data going through the nesdata and keyboarddata inputs are incremented with their specific clock signals off a shift register inside the inputted system. For nesdata specially this is done when the output neslatch goes high and it driven by the output nesclk. For the keyboarddata input a similar latch like signal is handled inside the keyboard\_press\_driver and keyboard\_inner\_driver as seen in figures 55 and 57. As discussed already the clockkeyboard is a clock cycle coming directly from the PS/2 keyboard. Unlike the other two inputs irdata is not driven by a clock signal but it is still however a binary signal that is constantly changing in a pattern to denote specific infrared signals. The IRreader block then takes that stream a parses through it as it comes in to ensure it can deliver the correct outputs for the given input stream.

Outputs: From top to bottom the outputs for this entire project are nesclk, neslatch, outcw, outcew, leddata, audioout, dig0, dig1, dig2, dig3, seg1, seg2, seg3, seg4, seg5, seg6, seg7, and seg8. As previously discussed in the inputs section above newlatch and newclk help driver the inputted data from the NES controller. This is done when neslatch is high and the newclk cycles, these two in combination allows for nesdata to receive a string of binary data that denotes which button is pressed. Neslatch goes high periodically to ensure that any button press it captured properly. Outcw and outcow work very similarly to each other. Together the driver DC motor that acts as one of the outputs for the overall project. When either go high the DC motor receives power to turn in either a clockwise direction or a counter clockwise direction depending on which output goes high. Due to controller limitations it is not possible for both to go high at the same time. Leddata acts as another waveform binary signal to demote specific output colors. To create specific colors on the LEDs twenty four bits of data are passed through the output leddata at specific timing frequencies. Similarly to leddata audioout is a waveform created with 1's and 0's at specific frequencies to give an audio device musical notes based on the key pressed on the PS/2 keyboard. Dig0 through dig3 are collections of 7 LEDs built into the FPGA that make up the 7-segment display units. Depending on the inputs given different LEDs are lit up to showcase the address and command code of the IR signal provided. Seg1 through seg 8 are more LEDs on the 7-segment display units that are used for error checking. When something goes wrong or an incorrect IR signal is taken through the irdata input, two of the 7-segment displays at the left end light with with a NE for "not equal".

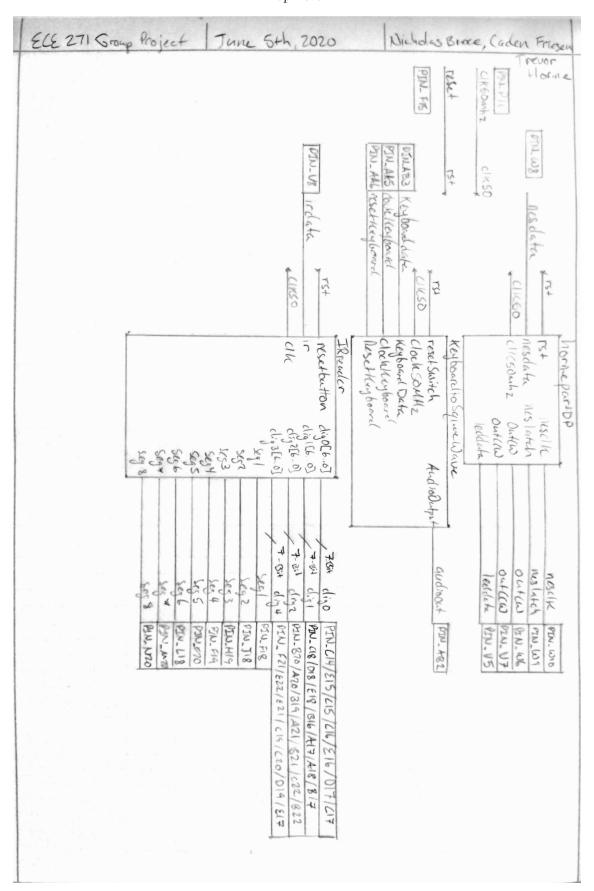

The design is shown at figure 1 on the following page.

Top Level

Figure 1

# 2 NES Controller Input - Motor and Addressable LED Output

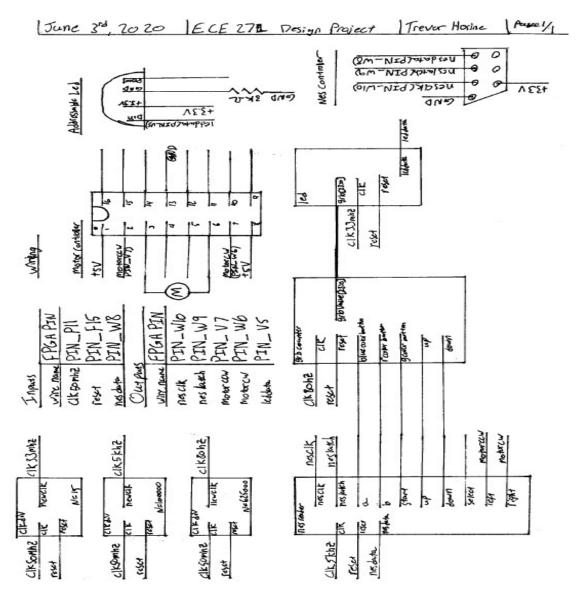

This section was implemented with a NES controller, addressable LED, and DC motor. The wiring diagrams can be found in figure 59 and the video of it in action can be found at the following link, https://youtu.be/PWSKQtm6lo0. Inputs: This part of the design project reads inputs from a NES controller and uses a switch and the 50MHz clock from the DE10-Lite FPGA.

Outputs: This module allows the user to control a motor and have it rotate clockwise when the right button on the d-pad of the NES controller is pressed and counter clockwise when the left button of the controller is pressed. In addition the addressable LED's RGB value can be controlled to a level of 0 to 255 for each color, red, green and blue. In order to increase a colors value hold that colors button, A for blue, B for red, and START for green, and use the up button on the d-pad. to decrease the color value for a color follow the same process but use the down button instead. The color values do roll over the top and bottom so the user can go from 0 to 255 by going down and from 255 to 0 by going up.

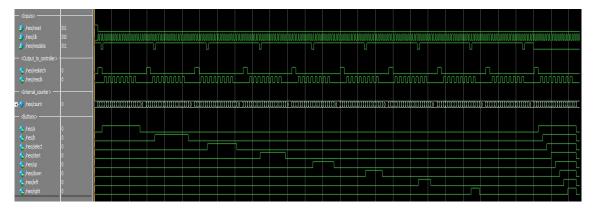

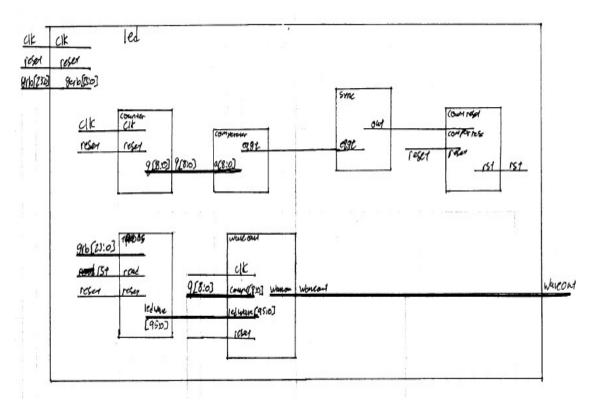

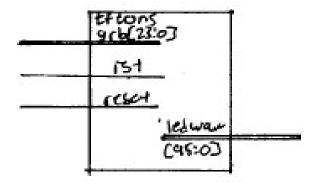

Figure 2: The top level design for the NES controller to addressable LED and motor.

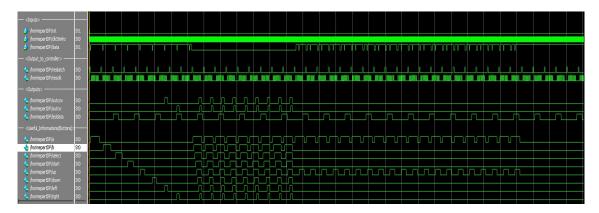

Figure 3: The top level simulation for the NES controller to addressable LED and motor.

#### 2.1 Clock Divider

Inputs: This block takes in a clock signal, 50MHz clock was used in the is project but this block will work with any. This block also has a active high reset. In addition this block has a parameter N.

Outputs: This block counts positive edges of the input clock until the counter matches the parameter N, then toggles the output clock. parameters  $N=15,\,100000,\,$  and 625000 are used in this sections of the project to obtain 3.3MHz, 5KHz, and 80Hz output clock signals respectively.

Figure 4: This is an block diagram for the clock divider.

Figure 5: This is an block diagram for the clock divider.

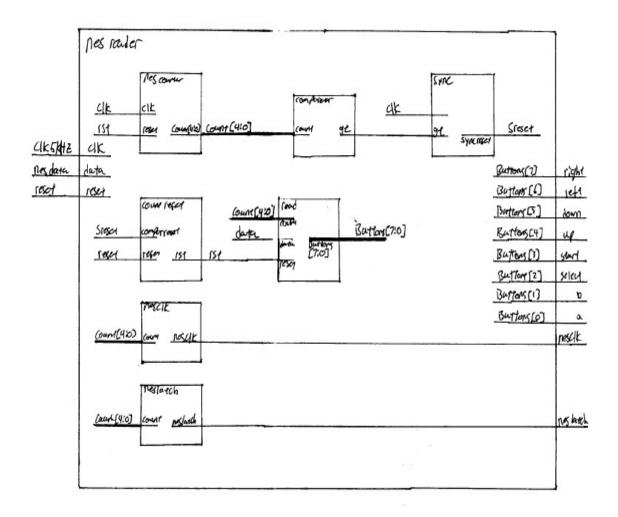

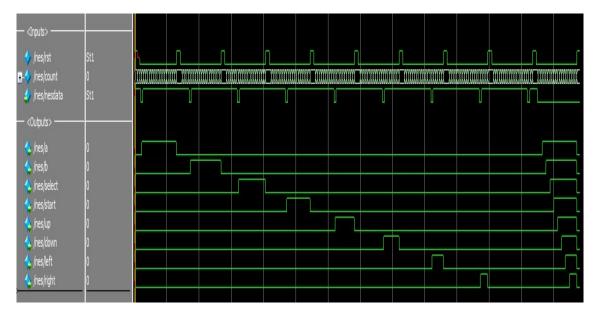

## 2.2 NES Reader

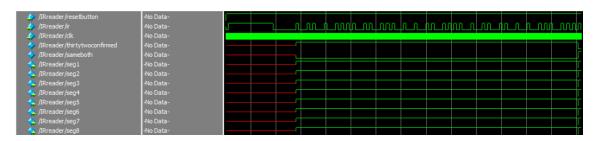

Inputs: This block takes in a clock signal, 5KHz clock was used in the is project, data from the NES controller, and a active high reset.

Outputs: This block reads the serial data pin from the NES controller and outputs all the buttons separately. This block also uses the input clock to drive the NES clock and latch pin. The NES latch pin tells the controller to load the current state of the buttons in to the controllers shift register, and NES clock shifts the bits out of the shift register through the NES data pin.

Figure 6: This is an block diagram for the NES reader.

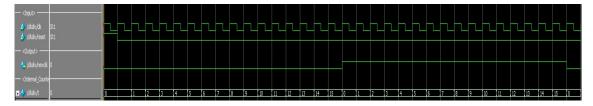

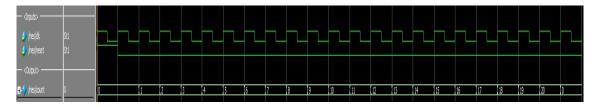

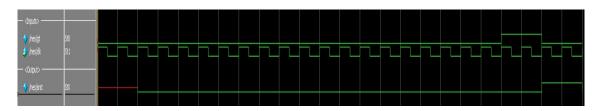

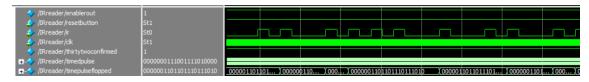

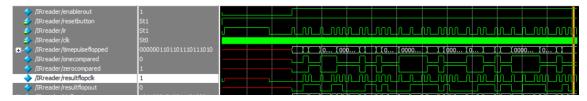

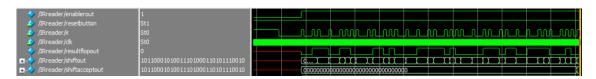

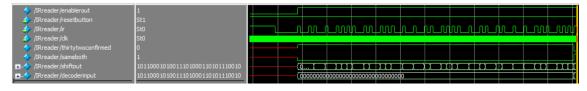

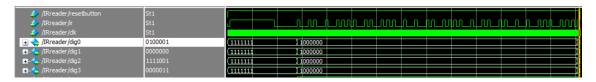

Figure 7: This is the simulation for the NES reader.

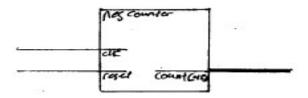

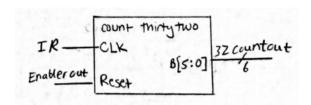

#### 2.2.1 NES Counter

The individual block shown in figure 8 uses the input clock, this project a 5KHz clock was used, to create a count that will be used to control the timing of thing with in the NES reader block.

Inputs: This block has two inputs, the  $5 \mathrm{KHz}$  clock signal used in the NES reader and the active high reset signal used with the NES reader.

Outputs: This block has one output called count, a 5 bit signal that counts up and is used in the timing of the NES reader block.

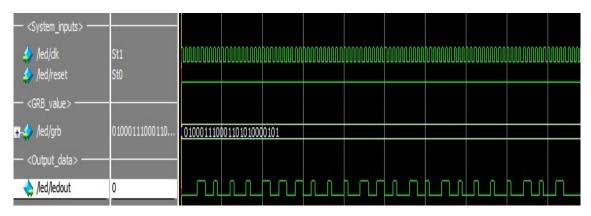

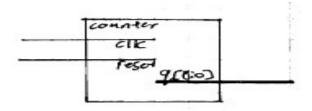

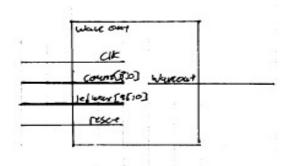

Figure 8: This block is a simple counter that counts up and is used in timing of the NES reader block.

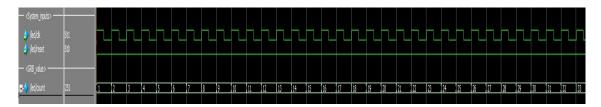

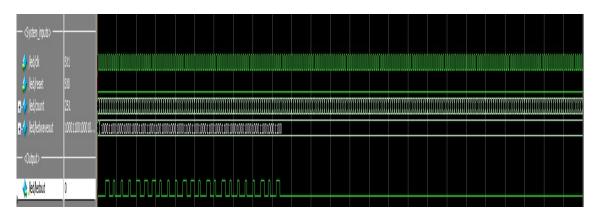

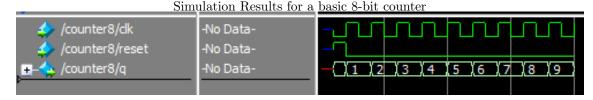

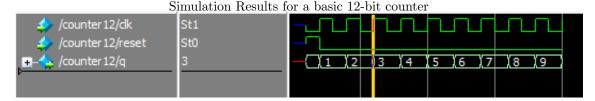

Figure 9: This is the simulation for a simple counter that counts up and is used in timing of the NES reader block.

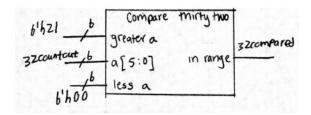

#### 2.2.2 Comparator

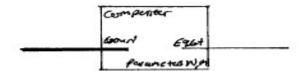

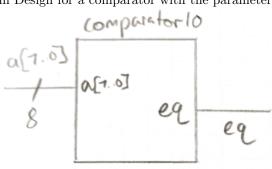

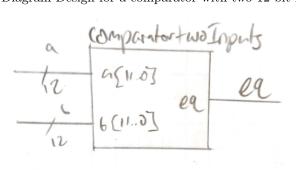

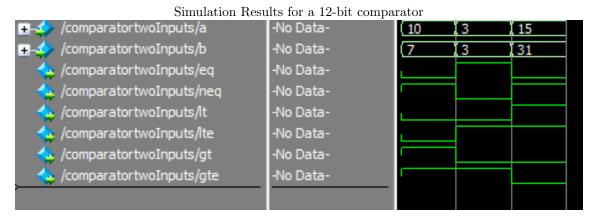

The individual block shown in figure 10 has one input, one output, and two parameters, N the number of bits in count and M the number count is being compared to.

Inputs: The input is the count from the counter in the nescounter block.

Outputs: The output is one if the input is greater then or equal to the second parameter M, and zero if it is not.

Figure 10: This block is a simple greater then or equal to comparator for the count from the nescounter block.

Figure 11: This is the simulation for a simple greater then or equal to comparator for the count from the nescounter block.

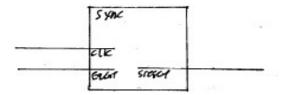

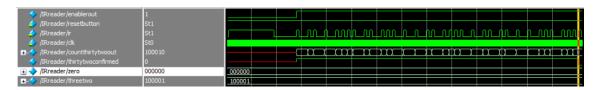

#### 2.2.3 Synchronizer

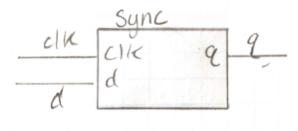

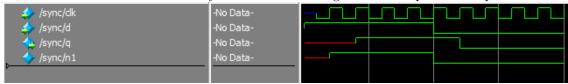

The individual block shown in figure 12 has two input the 5KHz clock and the output from the compartator. The output is a synchronized signal used as a reset for the counter.

Inputs: The inputs are the 5KHz clock and the output from the comparator block used to tell if the counter has reached a certain number.

Outputs: The output a synchronized signal that is used to reset the counter at the desired values that was specified by the M parameter in the comaprator.

Figure 12: This block is a simple syncronizer used in the reset of the counter.

Figure 13: This is the simulation for a simple syncronizer used in the reset of the counter.

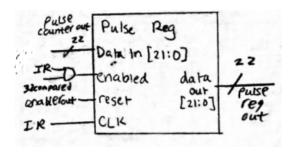

#### 2.2.4 Countreset

The individual block shown in figure 14 has two input and the one output, this block is essentially an OR gate.

Inputs: The inputs are the reset signal that is an input for the nesreader block and the output of the syncronizer.

Outputs: The output is a reset signal that is high where either input is high so the counter resets when the overall project reset is high or when it reaches its desired maximum set in the comaprator.

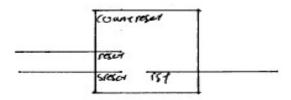

Figure 14: This block is simply an OR gate used to reset the counter.

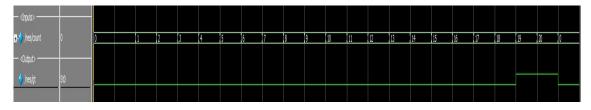

Figure 15: This is the simulation for countreset which is effectively an OR gate used to reset the counter.

### 2.2.5 Neslatch

The individual block shown in figure 16 has one input, count and one output neslatch. This block controls the latch signal that goes to the NES controller to load the data for the buttons in to the shift register in the controller.

Inputs: The input for this block is the 5 bit count from the nescounter.

Outputs: The output is a single bit latch signal that goes high to load data in to the shift register on the controller.

Figure 16: This block uses the counter for timing and outputs a high signal during certain sections of the count to load data in to the shift register of the controller.

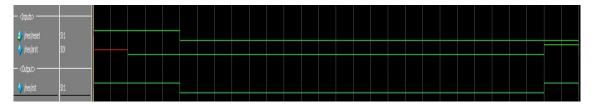

Figure 17: This is the simulation for neslatch module.

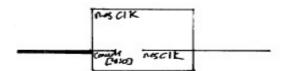

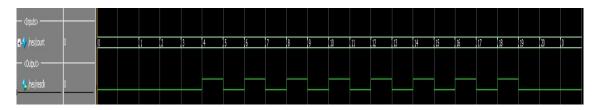

#### 2.2.6 Nesclk

The individual block shown in figure 18 has one input, count and one output nesclk. This block controls the clock signal that goes to the NES controller to shift the data for the buttons out of the shift register in the controller.

Inputs: The input for this block is the 5 bit count from the nescounter.

Outputs: The output is a single bit clock signal that goes high to shift data out through the data pin on the controller.

Figure 18: This block uses the counter for timing and outputs a high signal during certain sections of the count to shift data out though the data pin of the controller.

Figure 19: This is the simulation for nesclk module.

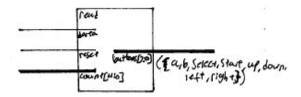

#### 2.2.7 Read

The individual block shown in figure 20 has three inputs, data, reset, and count. This block also has one output that is a bus containing all the information for the buttons that gets broken up to the various outputs of the nesreader.

Inputs: The inputs for this block is the 5 bit count from the nescounter, the data from the controller, and the overall project reset.

Outputs: The output is a eight bit signal that has the state of each button in a different bit. The output is then split in to each of the eight output of nesreader for the different buttons.

Figure 20: This block uses the counter for timing, and the data from the controller to output the state of each button.

Figure 21: This is the simulation for the read module.

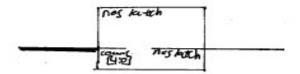

#### 2.3 Grbcounter

Inputs: This block takes in a clock signal, active high reset, up button, down button, and a button for each color red, green, and blue. When the up button and a color button are pressed at the same time that colors value from 0 to 255 is increased, when down and that colors button is pressed the value is decreased.

Outputs: the out put of this block is a 24 bit signal that contains the 0 to 255 value for green in the first eight bits, the value for red in the next eight bits, and the value for blue in the last eight bits.

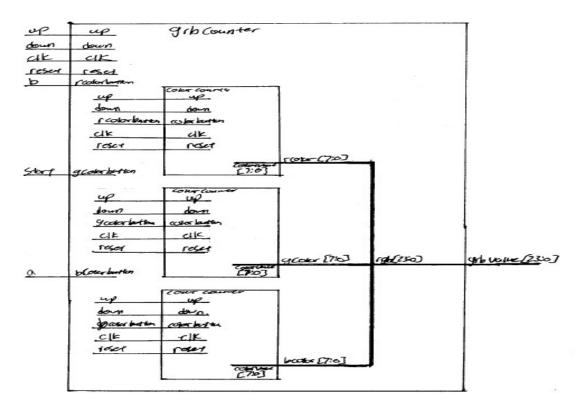

Figure 22: This is an block diagram for the grbcounter block.

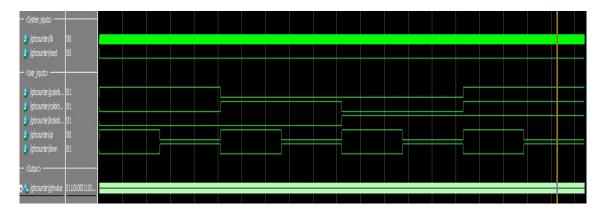

Figure 23: This is the simulation for the grbcounter block.

#### 2.3.1 Colorcounter

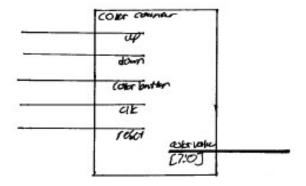

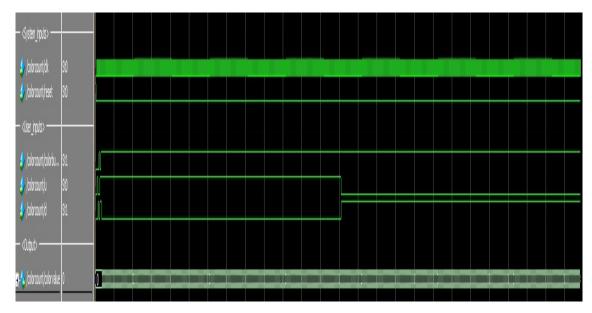

The individual block shown in figure ?? has five inputs, a clock signal, a active high reset, an up, a down, and a button signal. This block also has one output that is a eight bit bus containing the count of the counter for that color.

Inputs: The inputs for this block are the 80Hz clock signal provided to the grbcounter block, the active high reset of the overall project, a signal from the up button on the controller, a signal from the down button on the controller, and a signal from the button assigned to represent that color on the controller.